- 您现在的位置:买卖IC网 > Sheet目录457 > IXFR80N50Q3 (IXYS)MOSFET N-CH 500V 50A ISOPLUS247

IXFR80N50Q3

120

100

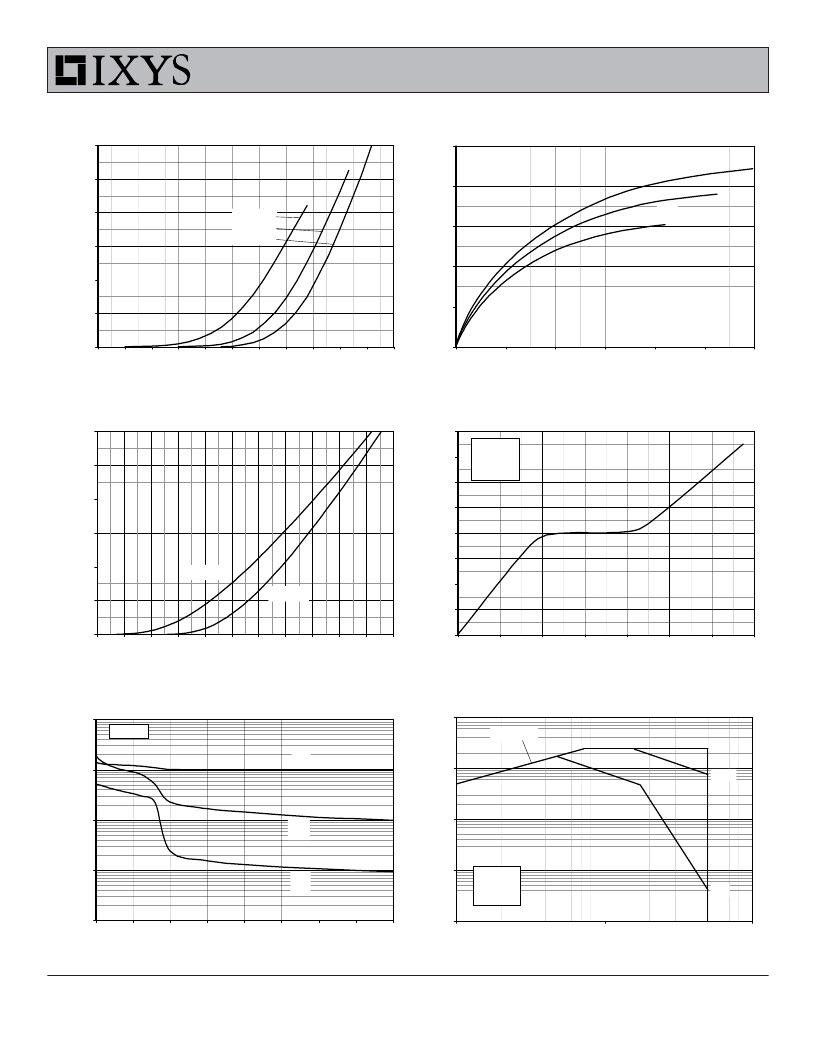

Fig. 7. Input Admittance

100

80

Fig. 8. Transconductance

T J = - 40oC

80

T J = 125oC

25oC

25oC

- 40oC

60

125oC

60

40

40

20

0

20

0

4.5

5.0

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

0

20

40

60

80

100

120

240

V GS - Volts

Fig. 9. Forward Voltage Drop of Intrinsic Diode

16

V DS = 250V

I D - Amperes

Fig. 10. Gate Charge

200

14

12

I D = 40A

I G = 10mA

160

10

120

80

40

0

T J = 125oC

T J = 25oC

8

6

4

2

0

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

1.1

1.2

1.3

1.4

0

40

80

120

160

200

240

280

100,000

f = 1 MHz

V SD - Volts

Fig. 11. Capacitance

1000

Q G - NanoCoulombs

Fig. 12. Forward-Bias Safe Operating Area

R DS(on) Limit

10,000

1,000

Ciss

100

10

100μs

Coss

100

Crss

1

T J = 150oC

T C = 25oC

1ms

Single Pulse

10

0.1

0

5

10

15

20

25

30

35

40

10

100

1,000

V DS - Volts

IXYS Reserves the Right to Change Limits, Test Conditions, and Dimensions.

V DS - Volts

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IXFT120N15P

MOSFET N-CH 150V 120A TO-268

IXFT12N100Q

MOSFET N-CH 1000V 12A TO268

IXFT12N100

MOSFET N-CH 1000V 12A TO-268

IXFT12N90Q

MOSFET N-CH 900V 12A TO-268

IXFT13N80Q

MOSFET N-CH 800V 13A TO-268

IXFT140N10P

MOSFET N-CH 100V 140A TO-268

IXFT14N100

MOSFET N-CH 1000V 14A TO-268

IXFT14N80P

MOSFET N-CH 800V 14A TO-268

相关代理商/技术参数

IXFR80N60P3

功能描述:MOSFET Polar3 HiPerFET Power MOSFET RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IXFR90N20

功能描述:MOSFET 90 Amps 200V 0.025 Rds RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IXFR90N20Q

功能描述:MOSFET 90 Amps 200V 0.025 Rds RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IXFR90N30

功能描述:MOSFET 75 Amps 300V 0.033 Rds RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IXFR9N80Q

功能描述:MOSFET 9 Amps 800V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IXFT10N100

功能描述:MOSFET 10 Amps 1000V 1.2 Rds RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IXFT10N100Q

制造商:IXYS 制造商全称:IXYS Corporation 功能描述:HiPerFETTM Power MOSFETs Q Class

IXFT120N15P

功能描述:MOSFET 120 Amps 150V 0.016 Rds RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube